哪里有MOS一体化

关键词: 哪里有MOS一体化 MOS

2026.03.17

2026.03.17

文章来源:

MOSFET的静态特性测试是评估器件性能的基础,需通过专业设备(如半导体参数分析仪)测量关键参数,确保器件符合设计规范。静态特性测试主要包括阈值电压Vth测试、导通电阻Rds(on)测试与转移特性测试。Vth测试需在特定Vds与Id条件下(如Vds=0.1V,Id=10μA),测量使Id达到设定值的Vgs,判断是否在规格范围内(通常为1V-5V),Vth偏移过大会导致电路导通异常。Rds(on)测试需在额定Vgs(如10V)与额定Id下,测量源漏之间的电压降Vds,通过R=V/I计算导通电阻,需确保Rds(on)小于较大值(如几十毫欧),避免导通损耗过大。

转移特性测试则是在固定Vds下,测量Id随Vgs的变化曲线,评估器件的电流控制能力:曲线斜率越大,跨导gm越高,放大能力越强;饱和区的Id稳定性则反映器件的线性度。静态测试需在不同温度下进行(如-40℃、25℃、125℃),评估温度对参数的影响,确保器件在全温范围内稳定工作。 上海贝岭 MOSFET 与瑞阳微产品形成互补,丰富客户选型范围。哪里有MOS一体化

MOS 的性能优劣由一系列关键参数量化,这些参数直接决定其场景适配能力。导通电阻(Rdson)是重心参数之一,指器件导通时源极与漏极之间的电阻,通常低至毫欧级,Rdson 越小,导通损耗越低,越适合大电流场景;开关速度由开通时间(tr)与关断时间(tf)衡量,纳秒级的开关速度是高频应用(如快充、高频逆变器)的重心要求;阈值电压(Vth)是开启导电沟道的相当小栅极电压,范围通常 1-4V,Vth 过高会增加驱动功耗,过低则易受干扰导致误触发;漏电流(Ioff)指器件关断时的漏泄电流,皮安级的漏电流能降低待机功耗,适配便携设备需求;击穿电压(BVdss)是源漏极之间的比较大耐压值,从几十伏到上千伏不等,高压 MOS(600V 以上)适配工业电源、新能源场景,低压 MOS(60V 以下)适用于消费电子。此外,结温范围(通常 - 55℃-150℃)、栅极电荷(Qg)、输出电容(Coss)等参数也需重点考量,例如 Qg 越小,驱动损耗越低,越适合高频开关。安徽kos-mos瑞阳微 RS30120 MOSFET 额定电流大,适配重型设备功率驱动需求。

MOS 的应用可靠性需通过器件选型、电路设计与防护措施多维度保障,避免因设计不当导致器件损坏或性能失效。首先是静电防护(ESD),MOS 栅极绝缘层极薄(只几纳米),静电电压超过几十伏即可击穿,因此在电路设计中需增加 ESD 防护二极管、RC 吸收电路,焊接与存储过程中需采用防静电包装、接地操作;其次是驱动电路匹配,栅极电荷(Qg)与驱动电压需适配,驱动电阻过大易导致开关损耗增加,过小则可能引发振荡,需根据器件参数优化驱动电路;第三是热管理设计,大电流应用中 MOS 的导通损耗与开关损耗会转化为热量,结温过高会加速器件老化,需通过散热片、散热膏、PCB 铜皮优化等方式提升散热效率,确保结温控制在额定范围内;第四是过压过流保护,在电源电路中需增加 TVS 管(瞬态电压抑制器)、保险丝等元件,避免输入电压突变或负载短路导致 MOS 击穿;此外,PCB 布局需减少寄生电感与电容,避免高频应用中出现电压尖峰,影响器件稳定性。

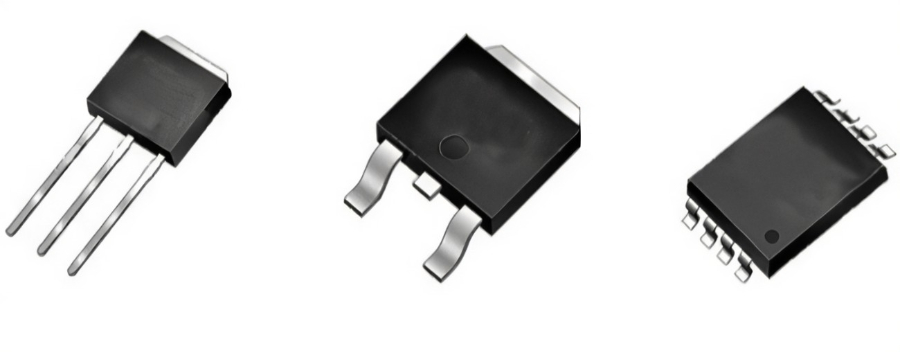

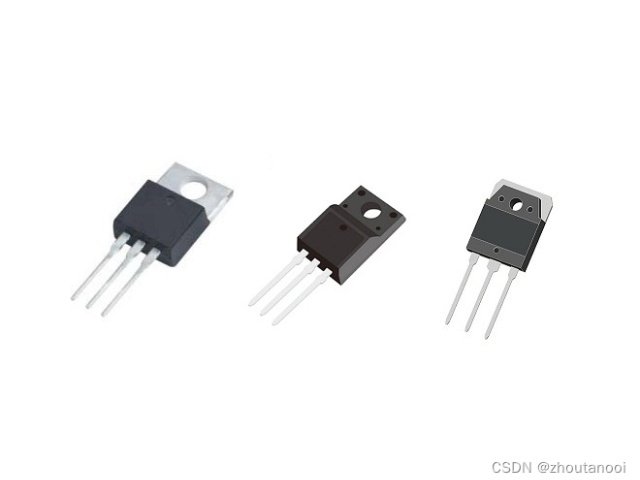

产品概述MOS管(金属氧化物半导体场效应晶体管,MOSFET)是一种以栅极电压控制电流的半导体器件,具有高输入阻抗、低功耗、高速开关等**优势,广泛应用于电源管理、电机驱动、消费电子、新能源等领域。其**结构由源极(S)、漏极(D)、栅极(G)和绝缘氧化层组成,通过栅压控制沟道导通,实现“开关”或“放大”功能。

分类按沟道类型:N沟道(NMOS):栅压正偏导通,导通电阻低,适合高电流场景(如快充、电机控制)。P沟道(PMOS):栅压负偏导通,常用于低电压反向控制(如电池保护、信号切换)。 瑞阳微 RS3407 MOSFET 静态功耗低,适合电池供电设备长期使用。

MOS 的性能特点呈现鲜明的场景依赖性,其优缺点在不同应用场景中被放大或弥补。重心优点包括:一是电压驱动特性,输入阻抗极高(10^12Ω 以上),栅极几乎不消耗电流,驱动电路简单、成本低,相比电流驱动的 BJT 优势明显;二是开关速度快,纳秒级的开关时间使其适配 100kHz 以上的高频场景,远超 IGBT 的开关速度;三是集成度高,平面结构与成熟工艺支持超大规模集成,单芯片可集成数十亿颗 MOS,是集成电路的重心单元;四是功耗低,低导通电阻与低漏电流结合,在消费电子、便携设备中能有效延长续航。其缺点也较为突出:一是耐压能力有限,传统硅基 MOS 的击穿电压多在 1500V 以下,无法适配特高压、超大功率场景(需依赖 IGBT 或宽禁带 MOS);二是通流能力相对较弱,大电流应用中需多器件并联,增加电路复杂度;三是抗静电能力差,栅极绝缘层极薄(纳米级),易被静电击穿,需额外做 ESD 防护设计。因此,MOS 更适配高频、低压、中大功率场景,与 IGBT、SiC 器件形成应用互补。士兰微 SVF9N90F MOSFET 耐压值高,是高压电源设备的理想选择。什么是MOS平均价格

瑞阳微 R55N10 MOSFET 散热性能优良,减少高温对设备的影响。哪里有MOS一体化

MOS 的重心结构由四部分构成:栅极(G)、源极(S)、漏极(D)与半导体衬底(Sub),整体呈层状堆叠设计。栅极通常由金属或多晶硅制成,通过一层极薄的氧化物绝缘层(传统为二氧化硅,厚度只纳米级)与衬底隔离,这也是 “绝缘栅” 的重心特征;源极和漏极是高浓度掺杂的半导体区域(N 型或 P 型),对称分布在栅极两侧,与衬底形成 PN 结;衬底为低掺杂半导体材料(硅基为主),是载流子(电子或空穴)运动的基础通道。根据衬底掺杂类型与沟道导电载流子差异,MOS 分为 N 沟道(电子导电)和 P 沟道(空穴导电)两类;按导通机制又可分为增强型(零栅压时无沟道,需加正向电压开启)和耗尽型(零栅压时已有沟道,加反向电压关断)。关键结构设计如绝缘层厚度、栅极面积、源漏间距,直接影响阈值电压、导通电阻与开关速度等重心性能。哪里有MOS一体化

- 美浦森IGBT 2026-03-18

- 哪里有IGBT价格对比 2026-03-17

- 哪里有MOS一体化 2026-03-17

- 自动IGBT价格走势 2026-03-17

- 质量MOS电话多少 2026-03-17

- 推广MOS资费 2026-03-17

- 现代化MOS代理品牌 2026-03-16

- 低价MOS成本价 2026-03-16

- 01 施迈赛CSS接近开关说明书

- 02 弹片价格咨询

- 03 安徽2.2uH一体成型电感服务电话

- 04 江苏九轴惯性传感器性能

- 05 辽宁晶闸管智能控制模块哪家好

- 06 抗静电esd

- 07 浙江AI box工业网关哪家好

- 08 上海医院弱电设计

- 09 江苏UV模压胶涂液产品介绍

- 10 黑龙江恒压晶闸管移相调压模块结构