深圳206封装时钟晶振推荐厂家

关键词: 深圳206封装时钟晶振推荐厂家 时钟晶振

2026.04.01

2026.04.01

文章来源:

时钟晶振的频率精度与稳定性,是系统长期可靠运行的基础。初始精度指在常温(如25°C)下,时钟晶振输出频率与标称值的偏差,通常以±ppm表示。而频率稳定性则包含了温度稳定性、电源电压稳定性、负载稳定性以及长期老化率等多重维度。温度稳定性尤为关键,因为设备工作环境温度会变化。一颗工业级时钟晶振需要在-40°C至+85°C范围内保持频率变化在±20ppm或更优。对于基站、光传输设备等室外应用,要求则更为严苛。此外,时钟晶振的输出频率会随供电电压的波动而变化,这种特性称为推频系数;也会因输出负载的变化而微调,称为负载牵引。品质好的时钟晶振会通过电路设计和工艺控制,将这些变化因素抑制在极小的范围内。低老化率则确保了在设备数年的使用寿命中,时钟基准不会发生明显的缓慢漂移。时钟晶振的老化率决定长期准确性。深圳206封装时钟晶振推荐厂家

MEMS(微机电系统)振荡器作为传统石英时钟晶振的技术竞争者,近年来取得了长足进步。MEMS振荡器采用半导体工艺在硅片上制造微型谐振器,并将振荡电路集成在同一芯片上。与传统石英时钟晶振相比,MEMS振荡器具有更强的抗冲击振动能力、更快的启动速度、更小的尺寸(可做到1.0mm x 0.8mm)以及更易于与CMOS工艺集成。然而,在高频、高稳定度和低相位噪声等性能指标上,好的石英时钟晶振目前仍保持着优势,尤其是在通信、测量等领域。两种技术路线将在未来长期共存与竞争,MEMS可能在消费电子和部分工业领域继续扩大份额,而石英时钟晶振凭借其成熟的工艺和好的性能,仍将在对时序性能有要求的市场中占据主导。罗湖区308封装时钟晶振厂家价格时钟晶振保证系统各部分协调工作。

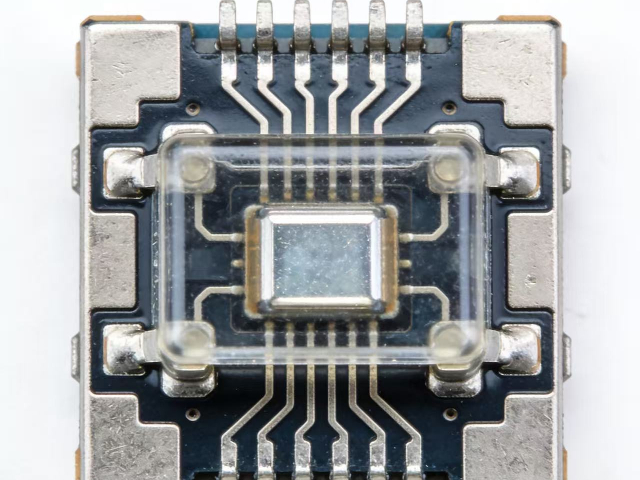

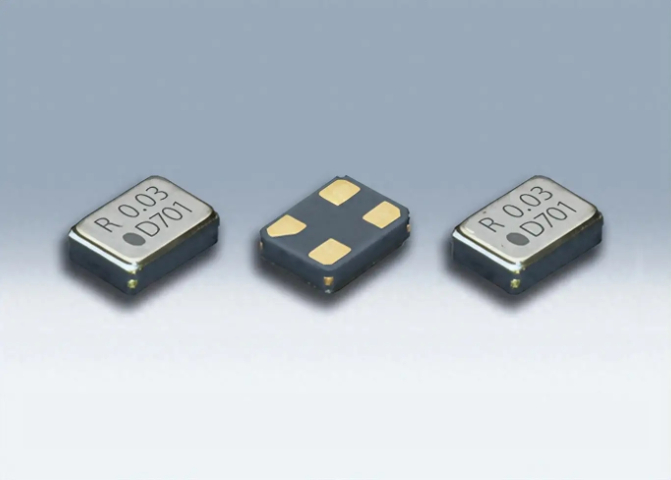

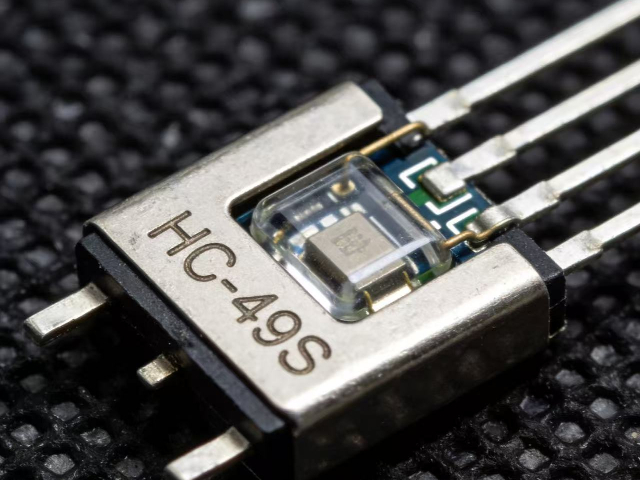

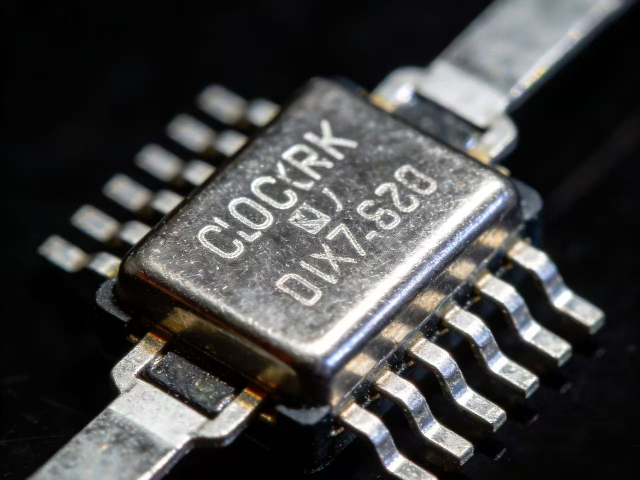

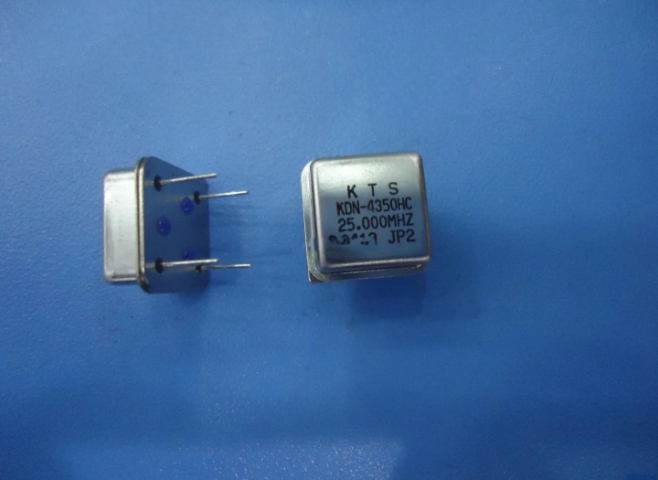

电子设备持续小型化的趋势,强力驱动着时钟晶振封装技术向微型化、高密度方向演进。从早期的全金属直插封装(如HC-49/U),到主流的表贴陶瓷封装,再到如今的芯片级尺寸封装,时钟晶振的占板面积不断缩小。3225(3.2mm x 2.5mm)、2520(2.5mm x 2.0mm)、2016(2.0mm x 1.6mm)已成为消费和通用工业领域的主流尺寸,而1612(1.6mm x 1.2mm)及更小的1008(1.0mm x 0.8mm)封装则面向可穿戴设备、超薄手机等极限空间应用。微型化封装带来了散热、密封性、抗机械应力及维持高Q值振荡等多重挑战。解决方案包括采用导热性更好的封装材料、更精密的内部结构设计、以及晶圆级封装等先进工艺。同时,将简单的时钟缓冲、电平转换或滤波功能与时钟晶振集成于单一封装的“时钟发生器”模块也日益普及,在提供稳定时钟源的同时,进一步节省了PCB空间,简化了外围电路设计。

随着处理器内核频率和高速接口速率不断攀升,时钟晶振的输出频率及其谐波进入更高频段,对PCB信号完整性设计提出严峻挑战。高频时钟信号对传输线损耗、阻抗不连续性、串扰和反射极为敏感。设计时必须将时钟走线视为受控阻抗传输线(通常50Ω单端或100Ω差分),使用合适的层叠结构,保持走线下方有完整、无分割的参考平面,并严格控制走线长度以管理时延和偏斜。在时钟晶振输出端和接收端,可能需要添加串联电阻或端接电阻来匹配阻抗,减少反射。对于差分时钟,应确保正负走线严格等长、等间距。良好的布局布线是保证高频时钟晶振性能在PCB上得以真实再现、避免信号劣化的且至关重要的一环,需要借助仿真工具进行预先分析和验证。低功耗时钟晶振适用于物联网设备。

时钟晶振的负载匹配与电路布局是保证信号完整性的实践关键。对于CMOS输出的时钟晶振,其数据手册会明确规定最大负载电容。实际电路中的总负载电容包括接收芯片的输入电容、PCB走线的寄生电容以及可能的外接匹配电容。若总负载超出允许范围,会导致时钟信号边沿变得圆滑,上升/下降时间延长,增加开关功耗,并在高频下可能引起振铃,严重时会影响时序裕量。最佳实践是:将时钟晶振尽量靠近主芯片的时钟输入引脚布局,使用短而直的走线,并确保下方有完整的地平面作为回流路径。避免在时钟线上打过孔或靠近其他高速信号线,以防止阻抗不连续和串扰。对于需要驱动多个负载或长距离传输的情况,务必使用专门的时钟缓冲器/驱动器进行扇出和信号重整,而不是让时钟晶振直接驱动。我们优化了时钟晶振的EMI性能。香洲区插件晶振时钟晶振批发

时钟晶振的电源需要良好去耦。深圳206封装时钟晶振推荐厂家

在复杂的多板卡、多芯片系统中,时钟分配网络的设计是确保全局同步的关键。此时,时钟晶振作为主时钟源,其信号需要通过时钟缓冲器、扇出驱动器或零延迟缓冲器分配到系统的各个角落。这就对时钟晶振的输出驱动能力和信号完整性提出了要求。一方面,时钟晶振需要具备足够的输出强度,以驱动后续缓冲器的输入电容和传输线的特征阻抗;另一方面,其输出信号的上升/下降时间、过冲与下冲必须得到良好控制,以防止在传输过程中产生过大的谐波辐射和反射。针对不同的负载需求,时钟晶振提供多种输出逻辑电平,如LVCMOS、LVDS、LVPECL、HCSL等。例如,LVDS输出的时钟晶振因其差分传输、低功耗、低抖动特性,常被用于驱动FPGA的高速串行收发器时钟。选择合适的输出类型,是保证时钟信号从源头到终端都保持高质量的重要一步。深圳206封装时钟晶振推荐厂家

深圳市鑫和顺科技有限公司在同行业领域中,一直处在一个不断锐意进取,不断制造创新的市场高度,多年以来致力于发展富有创新价值理念的产品标准,在广东省等地区的电子元器件中始终保持良好的商业口碑,成绩让我们喜悦,但不会让我们止步,残酷的市场磨炼了我们坚强不屈的意志,和谐温馨的工作环境,富有营养的公司土壤滋养着我们不断开拓创新,勇于进取的无限潜力,深圳市鑫和顺科技供应携手大家一起走向共同辉煌的未来,回首过去,我们不会因为取得了一点点成绩而沾沾自喜,相反的是面对竞争越来越激烈的市场氛围,我们更要明确自己的不足,做好迎接新挑战的准备,要不畏困难,激流勇进,以一个更崭新的精神面貌迎接大家,共同走向辉煌回来!

- 肇庆3068封装时钟晶振价格 2026-03-30

- 韶关音叉晶振RTC晶振 2026-03-30

- 汕头3215封装时钟晶振工厂 2026-03-30

- 浙江本地压控晶振价格 2026-03-30

- 河源SMD3068无源晶振售价 2026-03-30

- 汕尾无源晶振厂家价格 2026-03-30

- 山东标准温补晶振工厂 2026-03-30

- 通用压控晶振多少钱 2026-03-29

- 01 PI74FCT573TQEX

- 02 宿迁电感生产厂家

- 03 路西玛LUX9506 CMOS图像传感器参数

- 04 高良率电动工具方案定制

- 05 北京大功率制动单元哪家靠谱

- 06 江苏木工数控系统

- 07 贵州mosfet哪里有批发

- 08 三端稳压器输入两个电容

- 09 青海厂家直销显示屏价位

- 10 口碑好的阿尔法锡条供应商家