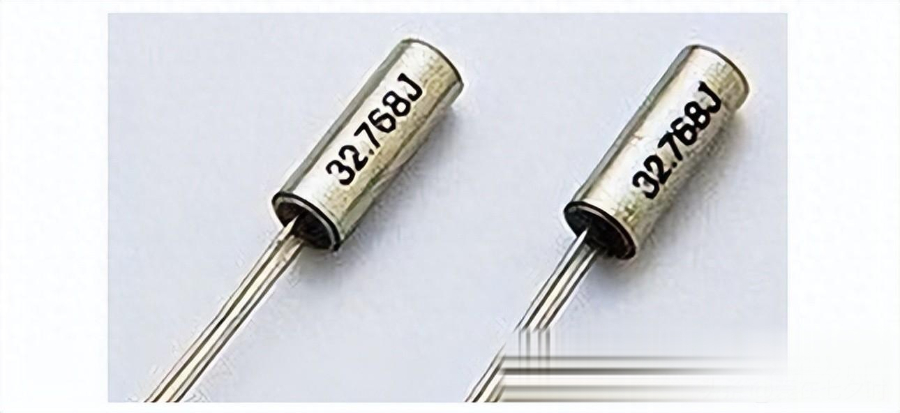

天河区32.768KHZ时钟晶振批发

关键词: 天河区32.768KHZ时钟晶振批发 时钟晶振

2026.04.20

2026.04.20

文章来源:

在专业音视频处理与传输设备中,时钟晶振负责为ADC/DAC、数字音频处理器、视频编解码器及显示接口提供主时钟。音频系统的音质对时钟抖动极为敏感,时钟抖动会通过数模转换过程直接引入非线性失真和本底噪声。因此,音频设备(如专业录音接口、数字调音台、Hi-Fi DAC)常采用低抖动的音频时钟晶振,其频率通常是音频采样率(如44.1kHz, 48kHz)的整数倍(如22.5792MHz, 24.576MHz)。在视频领域,像素时钟的稳定性与准确性决定了画面显示的同步性、刷新率精度和分辨率。例如,在HDMI 2.1发送器中,处理4K/8K高刷新率视频所需的时钟晶振必须具有极高的频率稳定性和极低的抖动,以确保无撕裂的高质量图像输出。多媒体应用对时钟的电磁兼容性设计也要求颇高,需防止时钟噪声干扰敏感的模拟信号通路。鑫和顺时钟晶振符合RoHS环保标准。天河区32.768KHZ时钟晶振批发

时钟晶振的相位噪声与时间抖动是衡量其性能的专业指标,对高速通信和精密测量系统尤为关键。相位噪声描述了理想时钟信号在频域上的能量扩散程度,表现为载波两侧的噪声边带;而时间抖动则是这种噪声在时域的直接体现,表现为时钟边沿相对于理想位置的随机偏移。在5G基站、高速SerDes(如PCIe 6.0, 800G以太网)等应用中,参考时钟晶振的相位噪声会直接转化为发射信号的带外杂散和接收机的噪声基底抬升,恶化系统信噪比与链路误码率。评估一颗时钟晶振时,工程师必须详细分析其在关键频偏点(如10Hz, 100Hz, 1kHz, 10kHz, 1MHz)的单边带相位噪声谱密度,以及在不同积分带宽下的随机抖动与确定性抖动。低相位噪声时钟晶振的设计,依赖于高Q值AT切晶体、低噪声振荡电路、精密的温度补偿或恒温控制技术,以及优异的电源噪声抑制能力。荔湾区时钟晶振鑫和顺时钟晶振支持多种工作电压。

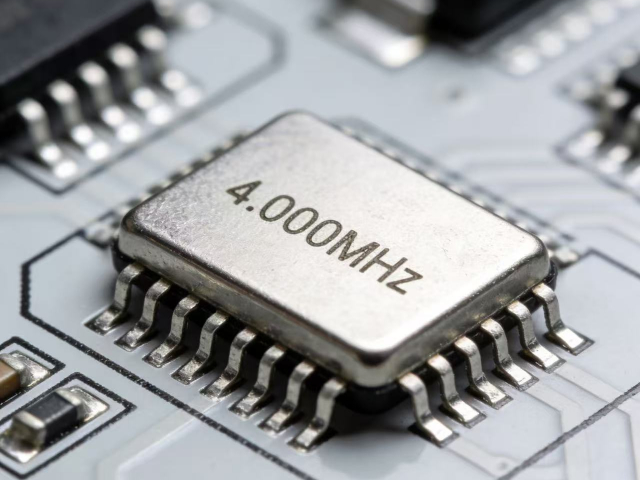

时钟晶振的负载匹配与电路布局是保证信号完整性的实践关键。对于CMOS输出的时钟晶振,其数据手册会明确规定最大负载电容。实际电路中的总负载电容包括接收芯片的输入电容、PCB走线的寄生电容以及可能的外接匹配电容。若总负载超出允许范围,会导致时钟信号边沿变得圆滑,上升/下降时间延长,增加开关功耗,并在高频下可能引起振铃,严重时会影响时序裕量。最佳实践是:将时钟晶振尽量靠近主芯片的时钟输入引脚布局,使用短而直的走线,并确保下方有完整的地平面作为回流路径。避免在时钟线上打过孔或靠近其他高速信号线,以防止阻抗不连续和串扰。对于需要驱动多个负载或长距离传输的情况,务必使用专门的时钟缓冲器/驱动器进行扇出和信号重整,而不是让时钟晶振直接驱动。

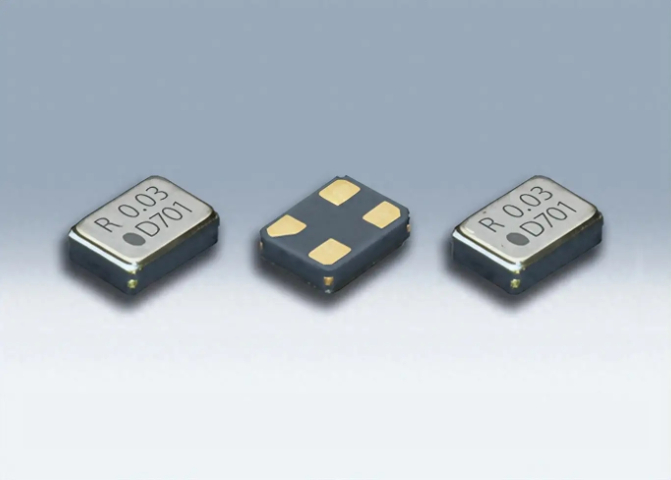

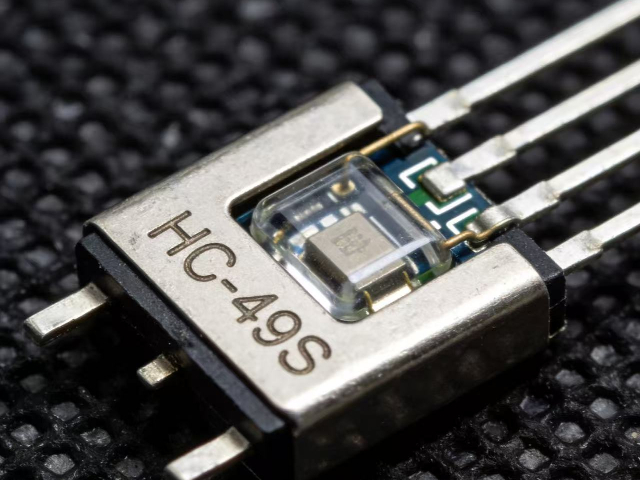

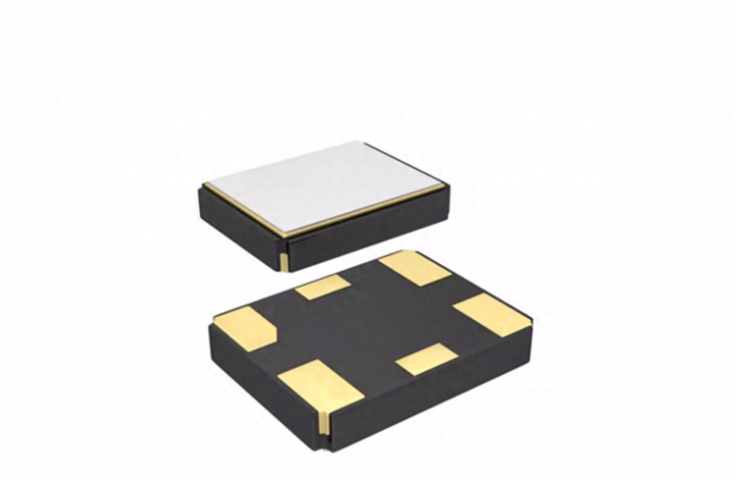

展望未来,时钟晶振技术将持续演进以应对新的系统挑战。在性能上,对更低相位噪声、更低抖动、更高频率和更优稳定性的追求永无止境。在集成度上,将时钟晶振与时钟发生器、抖动衰减器甚至特定功能芯片(如以太网PHY)封装在一起的系统级封装方案会越来越多。在智能化方面,支持动态频率调整、状态监控和数字配置的智能时钟晶振将更具吸引力。同时,新材料(如薄膜体声波谐振器)和新结构(如芯片级真空封装)的探索也在进行中。无论技术如何变化,时钟晶振作为电子系统同步与计时基础的地位不会改变。它将继续以更精湛的性能、更小的体积和更智能的方式,支撑起从消费电子到科技的宏大数字世界。高稳定时钟晶振确保数据同步传输。

随着处理器内核频率和高速接口速率不断攀升,时钟晶振的输出频率及其谐波进入更高频段,对PCB信号完整性设计提出严峻挑战。高频时钟信号对传输线损耗、阻抗不连续性、串扰和反射极为敏感。设计时必须将时钟走线视为受控阻抗传输线(通常50Ω单端或100Ω差分),使用合适的层叠结构,保持走线下方有完整、无分割的参考平面,并严格控制走线长度以管理时延和偏斜。在时钟晶振输出端和接收端,可能需要添加串联电阻或端接电阻来匹配阻抗,减少反射。对于差分时钟,应确保正负走线严格等长、等间距。良好的布局布线是保证高频时钟晶振性能在PCB上得以真实再现、避免信号劣化的且至关重要的一环,需要借助仿真工具进行预先分析和验证。我们的时钟晶振内置驱动增强电路。荔湾区时钟晶振

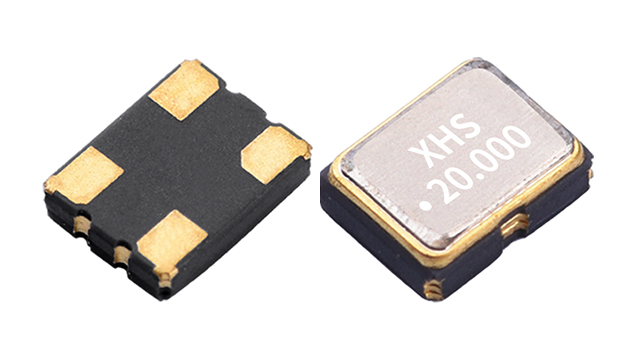

我们的时钟晶振提供CMOS输出电平。天河区32.768KHZ时钟晶振批发

时钟晶振的负载特性是电路匹配设计中的重要环节。对于CMOS输出的时钟晶振,其输出端可以等效为一个推挽输出的反相器。数据手册中通常会指定其大容性负载驱动能力,例如15pF或30pF。如果实际负载(包括芯片输入电容、PCB走线寄生电容等)超过此值,可能会导致输出波形边沿变缓、上升/下降时间增加,甚至引起振铃或额外的功耗,严重时可能影响时钟信号在接收端的采样建立/保持时间。因此,在布局布线时,应尽量缩短时钟晶振输出端到负载芯片输入端的走线距离,并避免在时钟线上打过孔或连接过多器件。对于驱动多个负载的情况,应使用专门的时钟缓冲器进行扇出,而非让时钟晶振直接驱动。天河区32.768KHZ时钟晶振批发

深圳市鑫和顺科技有限公司汇集了大量的优秀人才,集企业奇思,创经济奇迹,一群有梦想有朝气的团队不断在前进的道路上开创新天地,绘画新蓝图,在广东省等地区的电子元器件中始终保持良好的信誉,信奉着“争取每一个客户不容易,失去每一个用户很简单”的理念,市场是企业的方向,质量是企业的生命,在公司有效方针的领导下,全体上下,团结一致,共同进退,**协力把各方面工作做得更好,努力开创工作的新局面,公司的新高度,未来深圳市鑫和顺科技供应和您一起奔向更美好的未来,即使现在有一点小小的成绩,也不足以骄傲,过去的种种都已成为昨日我们只有总结经验,才能继续上路,让我们一起点燃新的希望,放飞新的梦想!

- 潮州无源晶振批量定制 2026-04-18

- 宝安区贴片晶振RTC晶振价格 2026-04-17

- 广东个性化压控晶振 2026-04-17

- 香洲区8233封装时钟晶振批量定制 2026-04-17

- 龙岗区时钟晶振时钟晶振生产 2026-04-16

- 荔湾区206封装时钟晶振生产 2026-04-16

- 上海个性化温补晶振批量定制 2026-04-16

- 肇庆32.768KHZ时钟晶振多少钱 2026-04-15

- 01 成都车库车牌识别屏设计

- 02 北京高分辨率电子束曝光推荐

- 03 上海BGA芯片PCBA加工组装

- 04 家用电器热熔断器

- 05 磁保持快速充电用继电器采购

- 06 南京算法类IP解决方案

- 07 内蒙古生产代理触摸屏出厂价格

- 08 中国台湾NTC热敏电阻一般多少钱

- 09 青海自动硅光芯片耦合测试系统机构

- 10 新疆研华主板ODM